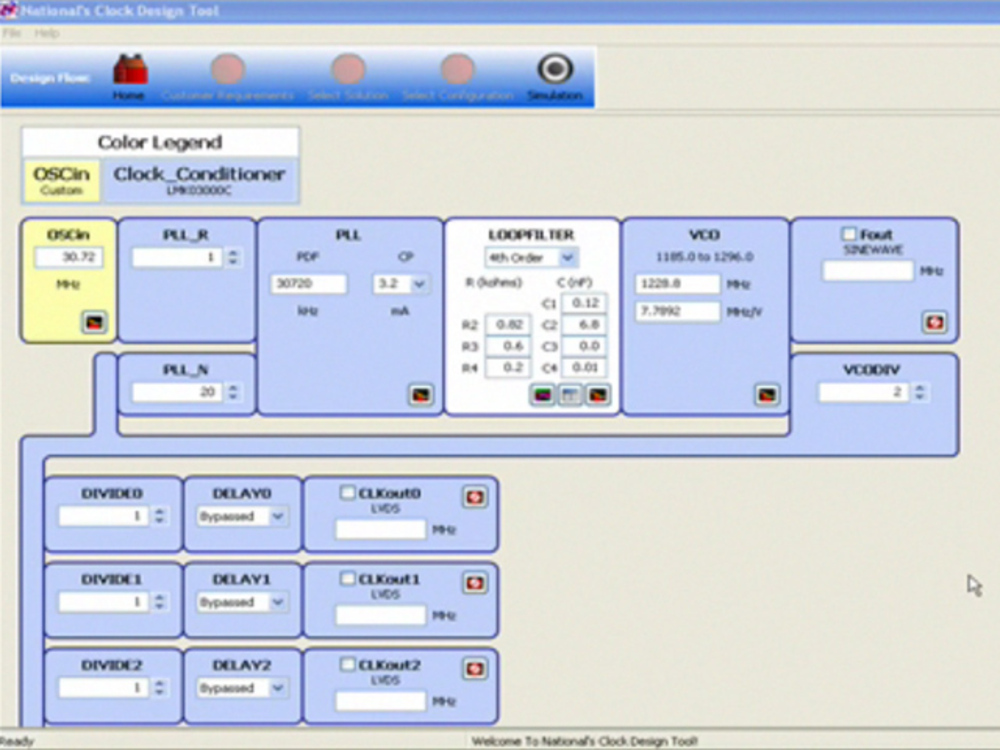

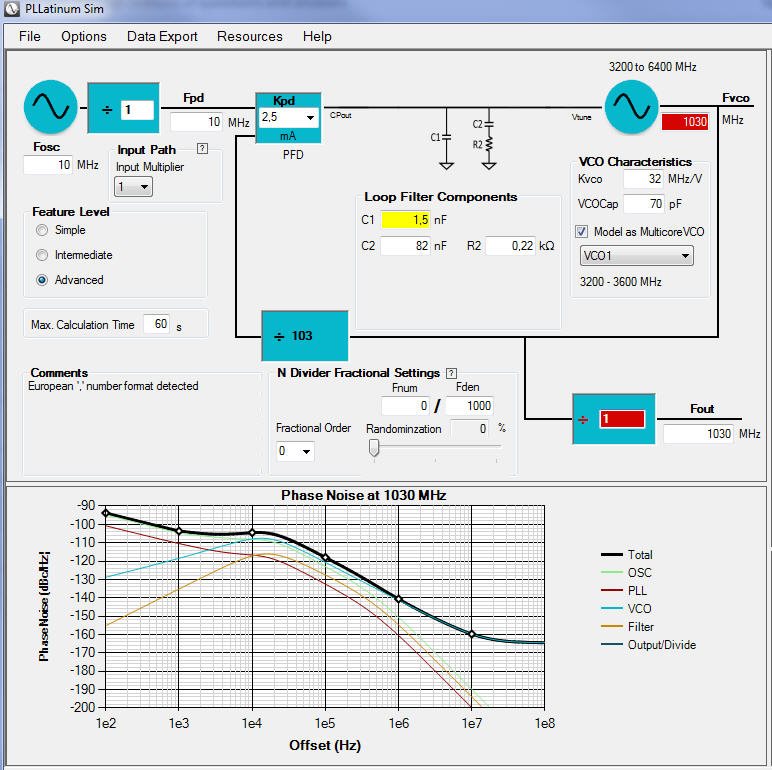

PLLatinum low power dual frequency synthesizer for RF. I simulate the PLL1 phase noise curves by typing below in clock design tool.

Phase Lock Loop Building Blocks Part 2 Ti Com Video

Filter design up for passive and active filters up to 4th-order.

. Soon students will be able to realize almost any analog system. Determining the design of a PLL usually means also determining the design of the loop filter which affects aspects of loop performance. Separate multiple terms with commas.

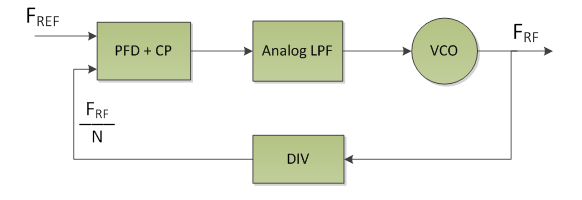

The Clock Design Tool software helps with part selection loop filter design and simulation of timing device solutions. 1R XTAL Kφ 1N VCO Fout Charge PumpPhase-Frequency Detector PFD Loop Filter. Learn how to calculate your gamma and PLL values quickly with the PLLatinum simulator tool.

Analog Devices Conducts Upcoming Webcasts on RF Design. Click on the PllDesign icon created during the installation process. When you enter desired output frequencies and a reference frequency optional the tool provides TI devices to meet the specified requirements divider values and a recommended loop filter to minimize jitter.

The Loop Calculator tool calculates component values for PLL loop filter design. Simply download the file setup_pll_designexe run it in Windows ie double click on it in Windows Explorer and then follow the setup instructions. Cost phase noise and package.

Using Eagleware now Agilent tools design a 400 MHz PLL. Learn more about PLL design with the PLL Performance Simulation and Design Handbook. Our RF PLLs and synthesizers help reduce your design time while exceeding performance requirements for applications such as aerospace defense.

The Clock Design Tool software helps with part selection loop filter design and simulation of timing device solutions. Interested in the latest news and articles about ADI products design tools training and events. Welcome to TIs Development Portal for Embedded Programming.

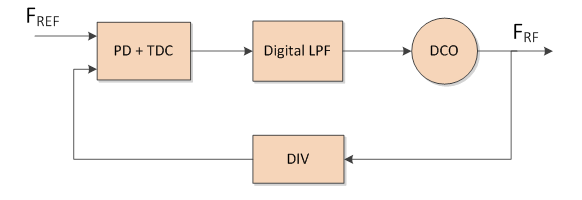

Analog Devices Debuts Industrys Highest Performing 13 GHz PLL Synthesizer. A PLL system consists of a stable and clean reference clock a PLL device and a loop filter followed by a voltage-controlled oscillator VCO. ADI HMC PLL Design Software Download.

This is because these components are difficult to integrate on a PLL synthesizer chip. The datasheet says the PN1Hz and PN10KHz of PLL1 as below. PLL Design Software is a powerful PLL design tool that enables users to accurately model and analyze performance of all HMC PLLs.

Reduce your testing time and get to the finished. Dean shows how to use tis clock design tool to quickly do pll loop filter design. PLL Design Software Version 11.

To run the program. Analog Devices 4-GHz PLL Synthesizer Offers Leading Phase Noise Performance. The ADIsimPLL design tool is a comprehensive and easy to use PLL synthesizer design and simulation tool.

Hi I have a problem with PLL design software. Instalation is succesful but problem is with MCR. It exhibits wide 300-MHz to 4800-MHz tuning range and a -132 dBcHz phase noise at 1-MHz offset of VCO frequency 2300-MHz enabling it to meet the.

Analog Devices Design Tools simplify your design and product selection process through ease of use and by simulating results that are optimized and tested for accuracy. The tool calculates component values based on system performance specifications. File directory in the PLL Design Modelszip file attached into the same directory where Hittite_PLL_Design_Toolexe is located which is.

Fully compatible with prior releases the ADIsimPLL design tool eliminates time. Thank you for your interest in the PLL Design Software. Texas Instruments PLLatinum Simulator Tool.

Download the LMX2592 data sheet. I have Matlab 2011 so i try instal new version 2015 problem. We offer a wide portfolio of RF phase-locked loops PLLs and synthesizers optimized for wideband high-speed applications with synchronization and normalized phase noise of less than 230 dBcHz.

The PLL Design Software is a powerful PLL design tool that enables users to accurately model and analyze performance of all Analog Devices HMC PLLs. Circuit Design Tools Calculators. As part of the lab course students will build analog systems using analog ICs and will study their macro models characteristics and limitations.

-With some files mat or pll it opens two or three windows same content. Note that the PLL technically refers to the entire system shown in figure 1 however sometimes the PLL is meant to refer to the entire system except for the crystal and VCO. Where you can develop online or download desktop tools including Code Composer Studio CCS.

TRF3720 a high-performance fully integrated IQ modulator and PLL synthesizer uses an external loop filter giving base station customers flexibility to design an application specific loop filter. Kindly can you please take some time to check if there any errors during my simulation. It allows users to communicate with PLL Evaluation Boards and observe test full functionality and performance of PLLs PLLs with Integrated VCO products.

- Unable to generate report it seems to. Analog Devices Wideband RF Synthesizers Feature System Size Reduction Design Versatility and Excellent Performance to 136 GHz. All key nonlinear effects that can impact PLL performance can be simulated including phase noise fractional-N spurs and anti-backlash pulse.

Typical PLL system block diagram. Simulation of phase noise including PLL fractional engine voltage-controlled oscillator VCO input dividers and loop filter. When you enter desired output frequencies and a reference frequency optional the tool provides TI devices to meet the specified requirements divider values and a recommended loop filter to minimize jitter.

Analog Devices Circuit Design tools are web based or downloadable but always free to use. I am struggling with the PLL phase noise simulation with clock design tool for LMK04828. Hi installed on Win 10.

The earlier version of HMC PLL Design V11 required MatLabs MCR V711 which was not readily available from MathWorks. PLL Design Software Version 104. The course can be adapted for either undergraduate or postgraduate curriculum.

View the TI LOOP_FILTER-CALC Calculation tool downloads description features and supporting documentation and start designing. Select Advanced in the Feature Level check box to unlock the gamma optimization parameter option. Tool Basics The PLL Design Assistant provides a graphical user interface methodology to the design of phase.

Ti clock design tool software is used to aid part selection loop filter des. A Phase-Locked Loop PLL is a closed-loop circuit that compares its output phase with the phase of an incoming reference signal and adjusts itself until both are aligned ie the PLL outputs phase is locked to that of the input reference. Choose from one of our 12 newsletters that match your product area of interest.

Lmx2492 Pllatinum Sim And Vss Lock Time Discrepancy Clock Timing Forum Clock Timing Ti E2e Support Forums

Phase Lock Loop Pll Bandwidth Design Part 2 Ti Com Video

Clock Design Tool Loop Filter Design Ti Com Video

Pll Synthesizers A Brief Overview Embedded Processing Technical Articles Ti E2e Support Forums

Pll Synthesizers A Brief Overview Embedded Processing Technical Articles Ti E2e Support Forums

Webench Tools Pllatinum Tool Pll Locking Tool Calculation Simulation Hardware System Design Tools Forum Simulation Hardware System Design Tools Ti E2e Support Forums

Webench Tools Lmx2572lp Ti Pll Platinum Sim Clock Timing Forum Clock Timing Ti E2e Support Forums

Why Component Integration Carries Weight For Space Based Pll Synthesizers Analog Technical Articles Ti E2e Support Forums

0 comments

Post a Comment